# Implementation of Various Logic Circuits and Evaluation by Power Efficiency

Siddhesh Posam<sup>1</sup>, Saurabh Tripathi<sup>2</sup>, Prof. Sonam Kandalgaonkar<sup>3</sup>

<sup>1</sup>(DepartmentofElectronics,AtharvaCollegeofEngineering,Malad-West,Mumbai-400095, <sup>2</sup>(DepartmentofElectronics,AtharvaCollegeofEngineering,Malad-West,Mumbai-400095, <sup>3</sup>(DepartmentofElectronics,AtharvaCollegeofEngineering,Malad-West,Mumbai-400095,

**Abstract:** The power dissipation in standard CMOS circuit can be decreased through adiabatic technique. By adiabatic technique dissipation in PMOS network may bedecreased and a few of energy keep at load capacitance may be recycled rather than dissipated as heat. however the adiabatic technique is extremely passionate about parameter variation. With the assistance of MICROWIND simulations, the energy consumption is analyzed by variation of parameter. In analysis, 2 logic families, ECRL (Efficient Charge Recovery Logic) and PFAL (Positive Feedback adiabatic Logic) area unitcompared with standard CMOS logic for electrical converter NAND and NOR circuits. it's finding that adiabatic technique is sweet alternative for low power application in nominative frequency vary.

**Keywords:** Power Consumption in CMOS, Equivalent Circuits, Four Phased Power Clock, Adiabatic Technique.

## I. Introduction

The term "adiabatic" describe the physical science processes within which no energy exchange with the atmosphere, and so no dissipated energy loss. However in VLSI, the electrical charge transfer between nodes of a circuit is taken into account because the method and numerous techniques may be applied to reduce the energy loss throughout charge transfer event. Absolutely adiabatic operation of a circuit is a perfect condition. It's going tobe solely achieved with terribly slow change speed. In sensible cases, energy dissipation with a charge transfer event consists of an adiabatic element and a non-adiabatic element. In standard CMOS logic circuits, from zero to VDD transition of the output node, the full output energy drawn from power offer and keep in electrical phenomenon network. adiabaticlogic circuits scale back the energy dissipation throughout change method, and utilize this energy by utilization from the load capacitance. For utilization, the adiabatic circuits use the constant current supply power offer and for scale back dissipation it uses the tetragon or curving power offer voltage. The equivalent circuit won't to model the standard CMOS circuits throughout charging method of the output load capacitance. However here constant voltage supply is replaced with the constant current supply to charge and discharge the output load capacitance. thus adiabatic change technique offers the less energy dissipation in PMOS network and reuses the keep energy within the output load capacitance by reversing the present supply. Adiabatic Logic doesn't dead switch from zero to VDD (and vice versa), however a voltage ramp is employed to charge and recover the energy from the output. adiabatic circuits area unitlow power circuits that use "reversible logic" to conserve energy. whereas this is often a district of active analysis, current techniques believe heavily on transmission gates and four-phased tetragon clocks to attain this goal.

### **II.** Proposed Method

#### **CMOSLogicalFamilies**:

Thetypesoflogiccircuitsare

- CMOSINVERTER

- CMOSNAND

- CMOSNOR

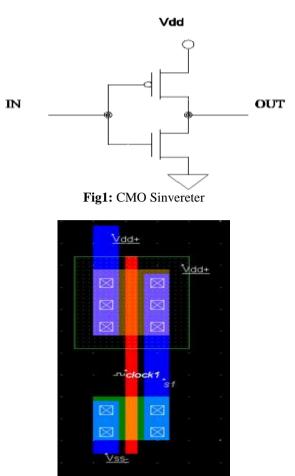

#### A. CMOSInverter

ThemostimportantCMOSgatelogicistheCMOSinverter.Itconsistsof solely 2 transistors, a try of1 N-typeandoneP-

type semiconductorunit.Asfig.1shows the essential circuit of CMOS electrical converter.Voltagelevels areau nitatlogical'1' equivalent to electrical evel VCC, alogical'0' (corresponding to 0 Vor GND).

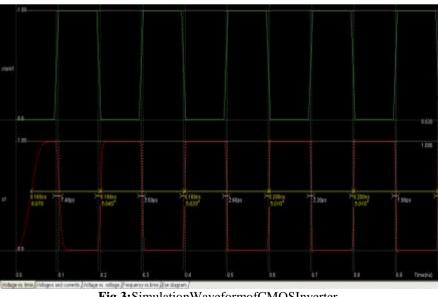

Fig.2: Layout Design of CMOS Inverter

Thelayout style of CMOS inverter isdrawn inkeeping with its circuit diagram as shown in fig. 2. Here, P MOSisinbrowncolor, NMOSisin inexperienced color, the metal 1 through that they're connected is blue incolor .Theredcolorshowspolysiliconlayer that isemployed togrant input.

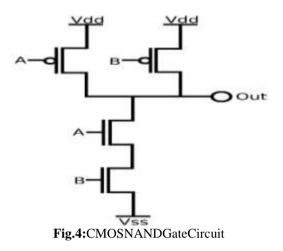

Fig.3:SimulationWaveformofCMOSInverter

In this simulation wave shape, it's noted that once input is 'High' the corresponding output is 'low'. CMOS NAND Circuit: A logic gate (Negated AND or NOT AND) may be a gate that produces AN output that's false provided that all its inputs area unit true. an occasional (0) output results provided that each the inputs to the gate area unit HIGH (1); if one or each inputs area unit LOW (0), a HIGH (1) output results. The logic gate is critical as a result of any Boolean perform may be enforced by employing a combination of NAND gates. This property is named purposeful completeness.

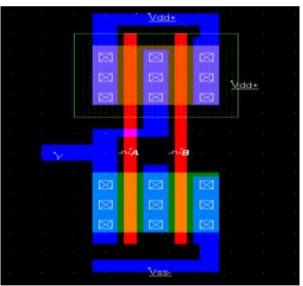

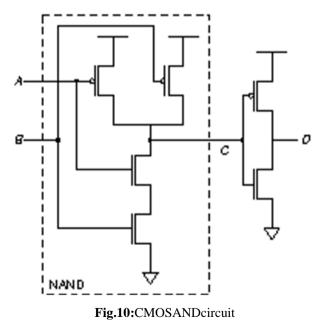

## **B. CMOSNANDCircuit:**

In CMOSNAND circuit, PMOS are connected in parallel and NMOS are connected in series.

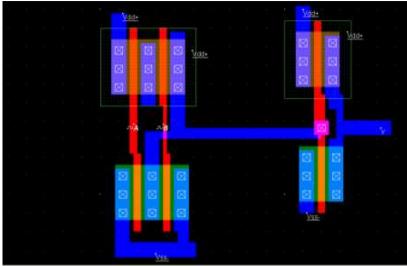

Fig.5:LayoutofCMOSNANDGate

The layout design of CMOSNAND gate is drawn according to its circuit diagram as shown in Fig. 4. In the two-input, NAND gate the P-type transistors are connected in parallel between VCC and the output, and the N-type transistors are connected in series from Vs stothe output.

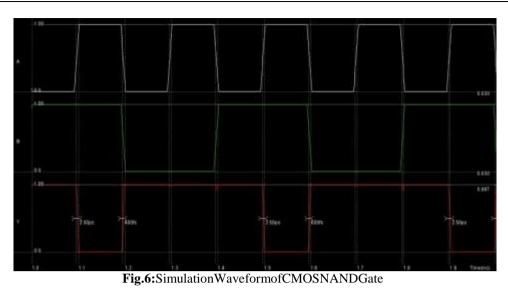

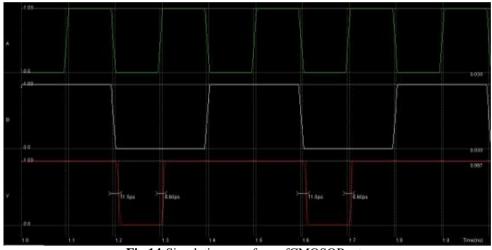

In the simulation wave form of CMOSNAND gate, it is seen that when both inputs are at `High', the corresponding output is `Low' and vice versa.

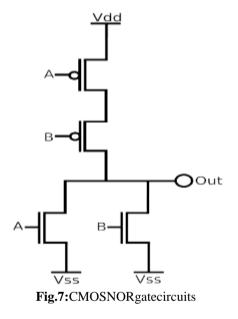

## C. CMOSNORCircuit:

TheNORgate maybea digital gate that implements logical NOR-

itbehaves inkeeping with the reality table to the proper. AHIGH output(1) results if each the inputs to the gate are a unit LOW(0); if one or each input is HIGH(1), an occasional output(0) results. neither is the results of the negation of the OR operator. It can even be seen as AN AND gate with all the inputs inverted. neither is a performally complete operation—

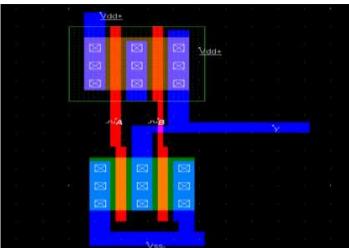

combinationsofNORgates maybe combined toget theotherlogicalfunction. againstthis,theORoperatorismo notonic becauseit will solelymodification LOWtoHIGH however not contrariwise.Thelayout style ofCMO S neitheris drawn inkeepingwith itscircuitdiagramasshowninfig.7. within the two-inputNORgatetheP-typetransistors areaunit connected asynchronous betweenVCC and also the output, whereas theN-typetransistors areaunit connected inparallelfromGNDtotheoutputY.

Fig.8:LayoutDesignofCMOSNORGate

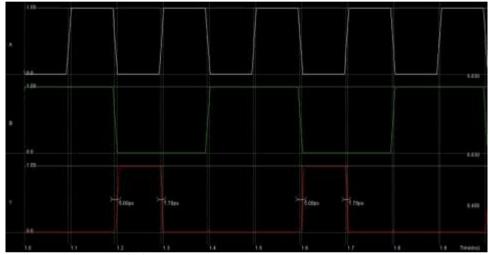

Fig.9: Simulation Waveform of CMOSNOR Gate

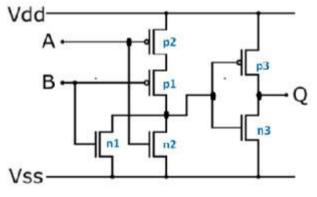

D. CMOSANDcircuit:

International Conference on Innovation and Advance Technologies in Engineering Atharva College of Engineering Malad Marve Road, Charkop Naka, Malad West Mumbai

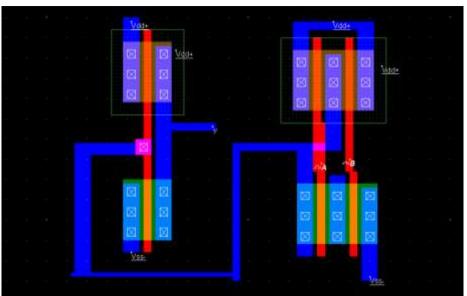

Fig.11: LayoutDesignofCMOSANDGate

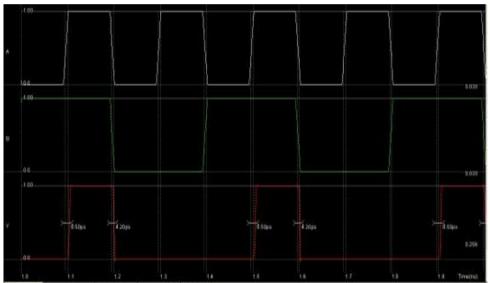

Fig.11:SimulationWaveformofCMOSNORGate

## E. CMOSORcircuit

Fig.12:CMOSORcircuit

Fig.13:LayoutdesignofCMOSORcircuit

Fig.14:SimulationwaveformofCMOSORgate

## III. Conlusion

The different parameter variations against cmos logic families area unit investigated, that shows that c moslogic families extremely dependent is parameter variations. however less energy consumption in cmos logic families may be still achieved with the help of the bigs election of parameter variations. NAND and NOR circuit ts shows higher energy savings than AND and OR at the high frequency and high load capacitance. Due to more trasi storare present in CMOS AND, CMOS OR circuits power consumption is more in that circuit over CMOS NAND, CMOS NOR gate circuits.

## **IV. FutureWork**

- Infuture, a diabatic logicare to be introduced which can help in overcoming the disadvantages of conventional CMOS logic circuits. For example-DFAL (Diode Free Adiabatic Logic Circuit).

- ForexamplewewillimplementINVERTER,NAND,NOR,AND,ORadiabticlogiccircuits

- Studyofcomparisonofadiabaticlogicsconnected with different types of multipliers in different parameters may also be done infuture.

- Futureworkalsoincludesthedesignoflargeradiabaticgatesandcircuitfromtheproposedbuffer/inverteranddissipa tedenergyanalysisathigherfrequenciesandcomparisonwithotheradiabaticfamilies.

#### References

- [1]. B.DilipKumarandM.Bharathi, "DesignofEnergyEfficientArithmeticCircuitsusingChargeRecoveryAdiabaticLogic", InternationalJour nalOfEngg.TrendsandTechnology,Vol.4,Issue-1,2013.

- P. Teichmann, "FundamentalsofAdiabaticLogics", lecture onAdiabaticLogic, SpringerSeries inAdvancedMicroelectronics 34, 2012. [2].

- [3]. JianpingHUandQiChen, "ModellingandNear-ThresholdComputingofPower-

- GatingAdiabaticLogicCircuit",Electricalreview,ISSN,2012.

- [4]. Nazrul Anvar, Toshikazu Sekine, "Fundamental Logic based on Two Phased Clocked Adiabatic Static CMOSLogic", IEEE journal of Semiconductor Technology and Science, Vol. 10, No. 1, 2009.

- LaszloVarga, FrenceKovacs, GaborHosszu, "An Efficient Adiabatic Charge Recovery Logic", IEEE papers, 2001. [5].

- [6]. [7].

- MuhammadArsalan,MaithamShams, "ComparativeAnalysisofAdiabaticLogicStyles",IEEEpapers,INMIC2004. YoungjoonShin,ChanhoLee,YoungMoon, "ALow-Power16-bitRISCMicroprocessorusingECRLCircuits",ETRIJournal,Vol.26,No.6,Dec.2004.